H5AN8G8NAFR-VKC,H5AN8G8NAFR-UHC,H5AN8G8NCJR-VKC,H5AN8G6NCJR-VKC是8Gb CMOS双倍数据速率IV(DDR4)同步DRAM,非常适合需要大存储密度和高带宽的主存储应用。SK hynix 8Gb DDR4 SDRAM提供完全同步的操作,参考时钟的上升沿和下降沿。当所有地址和控制输入都在CK的上升沿(CK的下降沿)上锁存时,数据,数据选通脉冲和写入数据掩码输入则在其上升沿和下降沿进行采样。数据路径在内部进行了流水线处理,并预取了8位以实现非常高的带宽。

特征

• VDD = VDDQ = 1.2V +/- 0.06V

• 完全差分时钟输入(CK,CK)操作

• 差分数据选通(DQS,DQS)

• 片上DLL将CK过渡对齐DQ,DQS和DQS过渡

• DM掩码在数据选通的上升沿和下降沿写入数据

• 所有地址和控制输入,除了在时钟的上升沿锁存的数据,数据选通和数据屏蔽

• 支持9、10、11、12、13、14、15、16、17、18、19和20的可编程CAS延迟

• 支持可编程的附加延迟0,CL-1和CL-2(仅x4 / x8)

• 可编程CAS写等待时间(CWL)= 9、10、11、12、14、16、18

• 可编程突发长度为4/8,具有半字节连续模式和交错模式

• BL即时切换

• 平均刷新周期(Tcase为0 oC〜95 oC)

-在0°C〜85°C 时为7.8 µs

-在85°C〜95°C时为3.9 µs

• JEDEC标准78球FBGA(x4 / x8),96球FBGA(x16)

• MRS选择的驾驶员力量

• 支持动态管芯端接

• 可以通过ODT引脚切换两个终止状态,例如RTT_PARK和RTT_NOM

• 支持异步RESET引脚

• 支持ZQ校准

• 支持TDQS(终端数据选通)(仅x8)

• 支持写均衡

• 8位预取

• 本产品符合RoHS指令。

• 内部Vref DQ电平生成可用

• 所有速度等级均支持写CRC

• 支持更大省电模式

• 支持TCAR(温度控制自动刷新)模式

• 支持LP ASR(低功耗自动自我刷新)模式

• 支持精细粒度刷新

• 支持每个DRAM可寻址性

• 支持减速模式(1/2速率,1/4速率)

• 支持用于读写的可编程序言

• 支持自刷新中止

• 支持CA奇偶校验(命令/地址奇偶校验)模式

• 应用了银行分组,并且具有相同或不同银行组访问权限的银行的CAS到CAS延迟(tCCD_L,tCCD_S)可用

• 支持DBI(数据总线反转)(x8)

H5AN8G8NAFR-VKC 技术数据表 规格书(PDF)

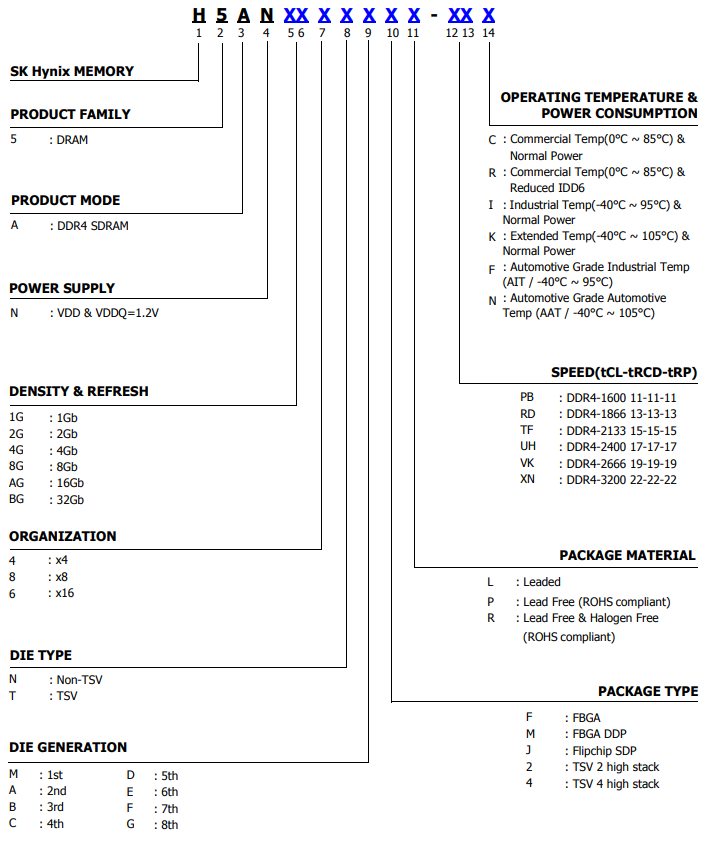

海力士SKhynix DDR4 DRAM 型号规则: